实验内容

设计一个8-3线优先编码器(74LS148);

设计一个3-8线译码器(74LS138)。

1. 设计一个8-3线优先编码器(74LS148) 实验原理:

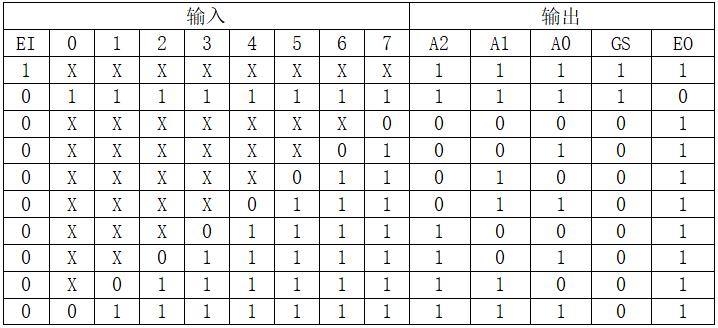

74LS148真值表

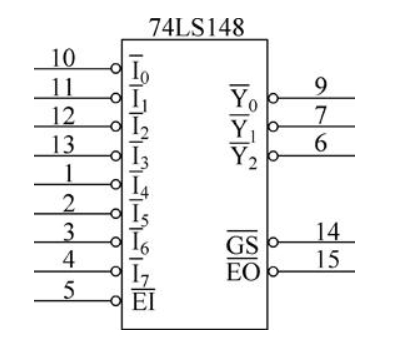

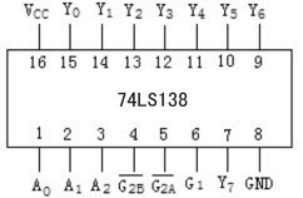

74LS148引脚图:

当使能端EI=0时,74LS148正常编码。位数越高优先级越高,输入输出均为正常逻辑的反向。输出为位值为‘0’的最高位所处位对应三位二进制数的取反。

实验模块代码:

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 32 LIBRARY IEEE; USE IEEE.STD_LOGIC_1164.ALL ;USE IEEE.STD_LOGIC_UNSIGNED.ALL ;ENTITY CD8_3 IS PORT (INPUT: IN STD_LOGIC_VECTOR (7 DOWNTO 0 ); EN: IN STD_LOGIC ; OUTPUT: OUT STD_LOGIC_VECTOR (2 DOWNTO 0 ); GS: OUT STD_LOGIC ; E0: OUT STD_LOGIC ); END ENTITY ;ARCHITECTURE BEHAV OF CD8_3 IS BEGIN PROCESS (INPUT,EN) BEGIN IF (EN='0' ) THEN IF (INPUT(7 ) = '0' ) THEN OUTPUT<="000" ; GS<='0' ;E0<='1' ; ELSIF (INPUT(6 ) = '0' ) THEN OUTPUT<="001" ; GS<='0' ;E0<='1' ; ELSIF (INPUT(5 ) = '0' ) THEN OUTPUT<="010" ; GS<='0' ;E0<='1' ; ELSIF (INPUT(4 ) = '0' ) THEN OUTPUT<="011" ; GS<='0' ;E0<='1' ; ELSIF (INPUT(3 ) = '0' ) THEN OUTPUT<="100" ; GS<='0' ;E0<='1' ; ELSIF (INPUT(2 ) = '0' ) THEN OUTPUT<="101" ; GS<='0' ;E0<='1' ; ELSIF (INPUT(1 ) = '0' ) THEN OUTPUT<="110" ; GS<='0' ;E0<='1' ; ELSIF (INPUT(0 ) = '0' ) THEN OUTPUT<="111" ; GS<='0' ;E0<='1' ; ELSE OUTPUT<="111" ; GS<='1' ;E0<='0' ; END IF ; ELSE OUTPUT<="111" ; GS<='1' ;E0<='1' ; END IF ; END PROCESS ; END ARCHITECTURE ;

TestBench:

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 32 33 34 35 36 37 LIBRARY ieee; USE ieee.std_logic_1164.all ; USE IEEE.STD_LOGIC_UNSIGNED.ALL ;ENTITY CD8_3_vhd_tst IS END CD8_3_vhd_tst;ARCHITECTURE CD8_3_arch OF CD8_3_vhd_tst IS SIGNAL E0 : STD_LOGIC ;SIGNAL EN : STD_LOGIC :='0' ;SIGNAL GS : STD_LOGIC ;SIGNAL INPUT : STD_LOGIC_VECTOR (7 DOWNTO 0 ) :="00000000" ;SIGNAL OUTPUT : STD_LOGIC_VECTOR (2 DOWNTO 0 );COMPONENT CD8_3 PORT ( E0 : OUT STD_LOGIC ; EN : IN STD_LOGIC ; GS : OUT STD_LOGIC ; INPUT : IN STD_LOGIC_VECTOR (7 DOWNTO 0 ); OUTPUT : OUT STD_LOGIC_VECTOR (2 DOWNTO 0 ) ); END COMPONENT ;BEGIN U1 : CD8_3 PORT MAP ( E0 => E0, EN => EN, GS => GS, INPUT => INPUT, OUTPUT => OUTPUT ); EN<= '0' , '1' AFTER 200 NS; INPUT <="10000000" , "00010000" AFTER 100 NS, "11111111" AFTER 150 NS, "00000011" AFTER 200 NS; END CD8_3_arch;

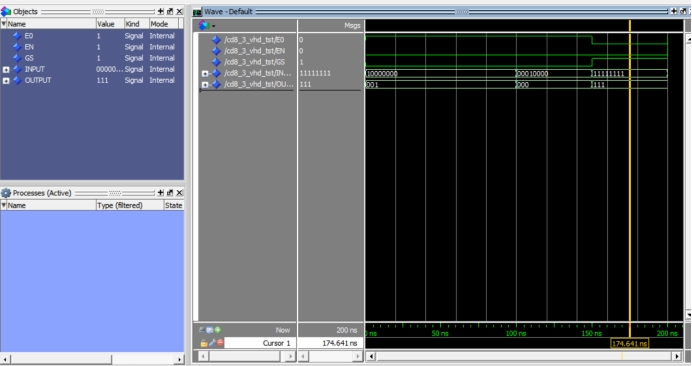

仿真波形图:

实验结果:按照74LS148引脚图,实验模块设计中输入输出均为取反的情况,对照真值表得到仿真结果正确。

2. 设计一个3-8线译码器(74LS138) 实验原理:

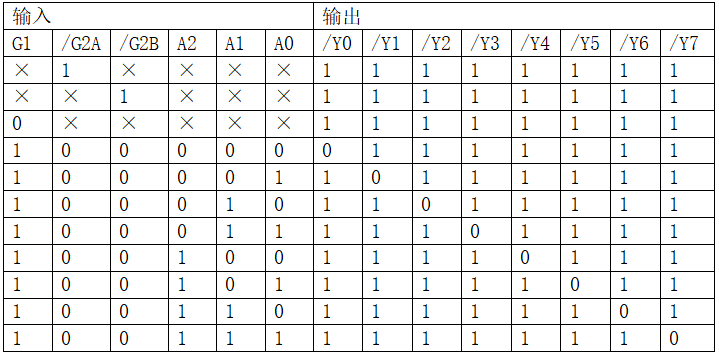

74LS138真值表

74LS138引脚图

当G1=1,/G2=0,/G3=0时,译码器正常译码,按照输入的3位二进制数,使输入对应数值的输出端口输出‘0’,其余输出‘1’(输出为正常逻辑的反向)。

实验模块代码:

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 32 33 34 LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL ;USE IEEE.STD_LOGIC_UNSIGNED.ALL ;ENTITY CD3_8 IS PORT (INPUT: IN STD_LOGIC_VECTOR (2 DOWNTO 0 ); G1: IN STD_LOGIC ; G2_FAN,G3_FAN: IN STD_LOGIC ; OUTPUT_FAN: OUT STD_LOGIC_VECTOR (7 DOWNTO 0 ) ); END ENTITY ;ARCHITECTURE BEHAV OF CD3_8 IS BEGIN PROCESS (INPUT,G1,G2_FAN,G3_FAN) BEGIN IF ((G1='1' ) AND (G2_FAN='0' ) AND (G3_FAN='0' )) THEN CASE INPUT IS WHEN "000" =>OUTPUT_FAN<="11111110" ; WHEN "001" =>OUTPUT_FAN<="11111101" ; WHEN "010" =>OUTPUT_FAN<="11111011" ; WHEN "011" =>OUTPUT_FAN<="11110111" ; WHEN "100" =>OUTPUT_FAN<="11101111" ; WHEN "101" =>OUTPUT_FAN<="11011111" ; WHEN "110" =>OUTPUT_FAN<="10111111" ; WHEN "111" =>OUTPUT_FAN<="01111111" ; WHEN OTHERS =>OUTPUT_FAN<="11111111" ; END CASE ; ELSE OUTPUT_FAN<="11111111" ; END IF ; END PROCESS ; END ARCHITECTURE ;

Testbench:

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 32 33 34 35 36 37 38 LIBRARY ieee; USE ieee.std_logic_1164.all ; ENTITY CD3_8_vhd_tst IS END CD3_8_vhd_tst;ARCHITECTURE CD3_8_arch OF CD3_8_vhd_tst IS SIGNAL G1 : STD_LOGIC :='1' ;SIGNAL G2_FAN : STD_LOGIC :='0' ;SIGNAL G3_FAN : STD_LOGIC :='0' ;SIGNAL INPUT : STD_LOGIC_VECTOR (2 DOWNTO 0 ):="000" ;SIGNAL OUTPUT_FAN : STD_LOGIC_VECTOR (7 DOWNTO 0 );COMPONENT CD3_8 PORT ( G1 : IN STD_LOGIC ; G2_FAN : IN STD_LOGIC ; G3_FAN : IN STD_LOGIC ; INPUT : IN STD_LOGIC_VECTOR (2 DOWNTO 0 ); OUTPUT_FAN : OUT STD_LOGIC_VECTOR (7 DOWNTO 0 ) ); END COMPONENT ;BEGIN u1 : CD3_8 PORT MAP ( G1 => G1, G2_FAN => G2_FAN, G3_FAN => G3_FAN, INPUT => INPUT, OUTPUT_FAN => OUTPUT_FAN ); G1<= '1' , '0' AFTER 200 NS,'1' AFTER 250 NS; G2_FAN<='0' , '1' AFTER 200 NS,'0' AFTER 250 NS; G3_FAN<='0' ; INPUT <="010" , "101" AFTER 100 NS, "110" AFTER 150 NS, "111" AFTER 200 NS; END CD3_8_arch;

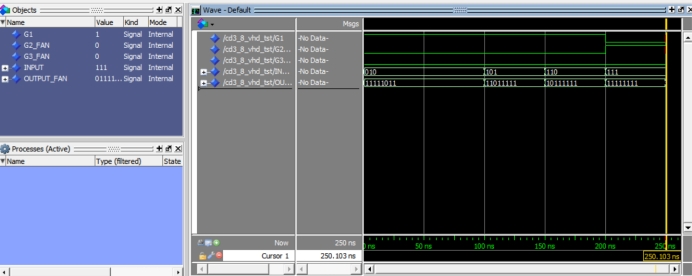

仿真波形:

实验结果:当G1=1,/G2=0,/G3=0时,译码正常;否则输出二进制码位全为‘1’。